D :: The Problematic Processor

Time Limit: 15 Seconds Memory Limit: 65536 KB

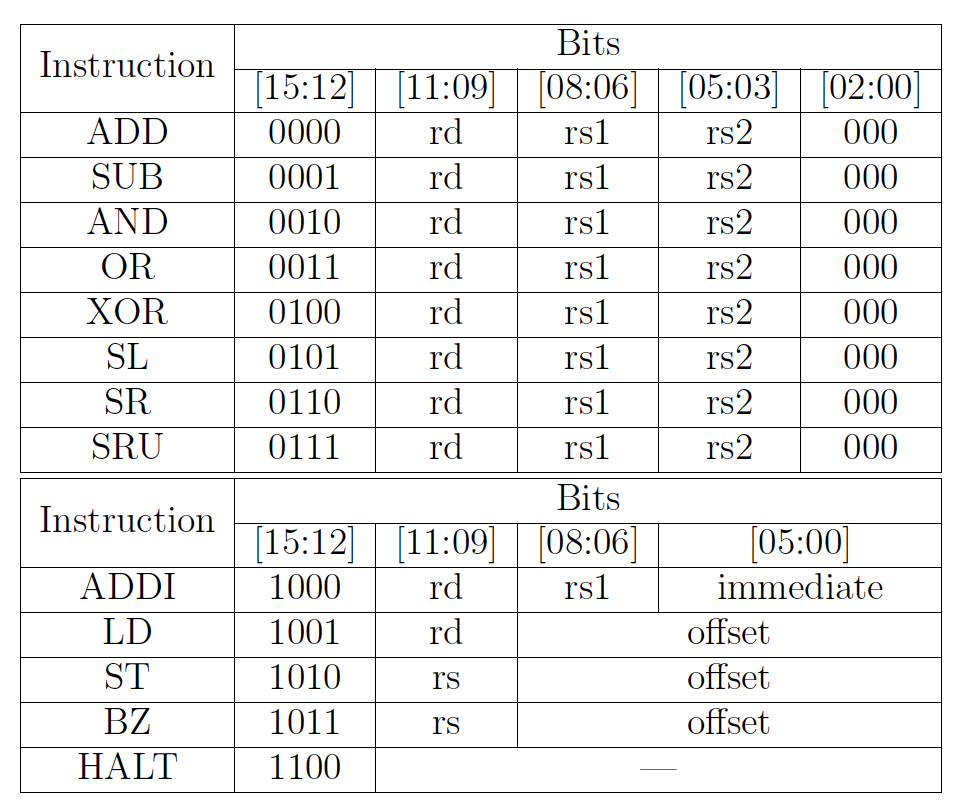

Laurel and Hardy have designed the new Intel Computer Processor for Charity (ICPC). This processor has 8 16-bit registers. Processor commands have 16 bits each. Authorized commands for the processor are as followed. (Register 0 constantly contains a 0 and no value can be saved in it.)

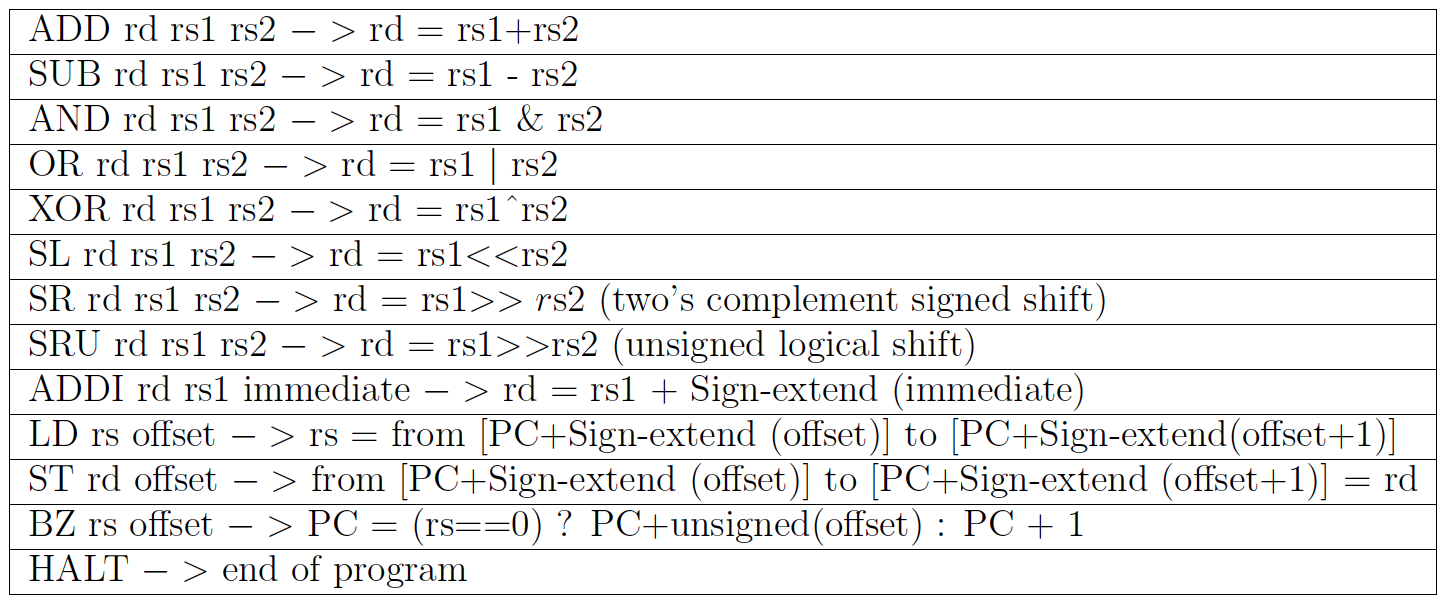

The operations executed in each command are explained below:

Note that the greater values are saved in the lesser bytes of the memory; e.g. for the command (LD 2 127), the 127th byte of the memory is saved in the 8 greater bits of register 2 and the 128th byte is saved in its 8 lesser bits. All registers have the initial value of 0. All the commands (with the exception of SRU) are executed with signed values and overflow is possible. No extra memory is allocated for the operations of ”load” and ”store” commands, these operations are instead executed in the commands’ memory.

However, the processor has faced some problems: For each register i there is a chance of pi that the data is not saved in the memory. Assuming you are given the values of pi and the memories, determine the correct value (i.e. assuming all the previous operations to be done correctly) and expected value of each of the registers at the end of the execution.

Also note that ”branch” and ”store” commands are executed on the correct values of the registers and not the incorrect ones.

Input

The input contains several test cases.

In the first line of input comes T (0 < T ≤ 32), the number of test cases.

For each test, the first line contains 7 numbers in the range of [0, 1] that represent the chance of registers 1 to 7 to be damaged. (Register 0 constantly contains a 0.)

The second line contains a number l (at most 1024) specifying the size of the memory in bytes. The input is followed in the next line by a string of length 2*l (consisting of the numbers 0 to 9 and characters A to F or a to f), each representing 4 bits of the memory (in hexadecimal).

Output

For each test, if there existed any errors in the code, print the error expressions; otherwise print in 7 separate lines the expected values of registers 1 to 7 respectively, each with 5 places of precision. Also print the correct values of these registers in the following 7 lines.

Print ”invalid operation” in case of receiving bad inputs for the commands. If access to invalid parts of the memory is requested, print ”segment fault”.

Sample Input

1 0.5 0.5 0.5 0.5 0.5 0.5 0.5 42 820184010650028004C00650028004C00650028004C00650028004C00650028004C00650028004C0C000

Sample Output

0.99512 1.43115 1.68848 0.00000 0.00000 0.00000 0.00000 13 21 21 0 0 0 0Submit

Source: 13th Iran Nationwide Internet Contest - UT